Displeja panelis, ko ražo LCD šķidro kristālu displejs, tiek plaši izmantots militārajā aprīkojumā. Šis dizains apstiprina Spartan-3E FPGA kā aparatūru. 2 un TImes, 16 rakstzīmju displejs ietver Sitronix ST7066U grafisko kontrolieri, lai realizētu LCD displeja raksturu vai ķīniešu raksturu. Pilnekrāna ekrāns, pilnekrāna mobilais displejs un viena rakstzīme displejs ekrānā. Visas funkcijas tiek īstenotas VHDL valodā, lai izpildītu LCD displeja prasības un panāktu dažādus ekrāna efektus.

LCD šķidro kristālu displeju dēļ tā ir mazs izmērs, viegls svars un mazs enerģijas patēriņš, ir plašs lietojumu klāsts. Piemēram, gaisa kuģu, tvertņu un kuģu displeju paneļi var samazināt sākotnējās CRT displeja platību, samazināt ierīces svaru un uzlabot mobilitāti.

Šajā dizainā Spartan-3E izstrādes panelī ir iebūvēts rakstzīmju ekrāns ar iebūvētu Si.tronix ST7066U grafisko kontrolieri, kas īsteno: (1) vienkrāsas displeju jebkurā pozīcijā un pilnekrāna un pilnekrāna rakstzīmju displeju; (2) Parasto rakstzīmju (rakstzīmju) un pilnekrāna kustības displeja parādīšana atsevišķām rakstzīmēm. Starp tiem grafisko kontrolieris [1] ir atbildīgs par vadības komandu un datu saņemšanu un nosūtīšanu uz LCD displeju.

1 Sitronix ST7066U grafisko kontrolieris

Kontrolierim ir trīs iekšējās atmiņas telpas, DD RAM, CGROM un CG RAM, kas pirms datu sūtīšanas jāiestata.

(1) DD RAM (displejs datu RAM)

Rakstzīmju kods tiek saglabāts. Fiziski DD RAM kopumā ir 80 rakstzīmju pozīcijas, katrā rindiņā ir 40 rakstzīmes, bet tikai 16 var tikt parādīti, un pārējie 24 netiek rādīti. Pirms lasīšanas vai rakstīšanas adreses skaitītājs ir jāiestata. Adreses skaitītāju var saglabāt nemainīgu vai automātiski palielināt vai samazināt par 1 pēc lasīšanas vai rakstīšanas.

(2) CG ROM (rakstzīmju ģeneratora ROM)

Fonta bitmap, kas satur katru iepriekš noteiktu rakstzīmi.

(3) CG RAM (rakstzīmju ģenerators RAM)

Satur 8 bitu pielāgotu rakstzīmju rindu attēlus. Katrs pielāgotais rakstzīmju bits sastāv no 5 punktiem 8 bitu kartēs. Konkrētais lietojums ir tāds pats kā DD RAM.

1.1 Saskarnes signāli ar FPGA

LCD un FPGA saskarnes signāli [2] ir: (1) iespējotu signālu LCD_E; (2) reģistrēties izvēlēties signālu LCD_RS; (3) lasīšanas / rakstīšanas vadības signāls LCD_RW; (4) četras LCD datu līnijas un StrataFlash datu līnija SF_D atkārtota izmantošana 11: 8.

1.2 Laika analīze

Datu vērtība SF_D 11: 8, LCD_RS, LCD_RW ir jānosaka un stabils vismaz 40 ns, pirms LCD_E iet augsts, un LCD_E paliek augsts vismaz 230 ns. Daudzās lietojumprogrammās LCD_RW vienmēr ir zems, jo dati parasti netiek nolasīti no displeja.

Kā parādīts 1. attēlā, dati tiek pārsūtīti 8 bitu formātā un ir sadalīti augstajos 4 bitiem un zemajos 4 bitiem. Pirmie augstie 4 biti un tad zemie 4 biti ir intervāli vismaz 1u. Pirms nākamās saziņas 8 bitu rakstīšanas operācijai ir minimālais intervāls 40 metijas, un pēc dzēšanas komandas aizkavēšanās jāpalielina līdz 1,64 ms.

FPGA bāzes LCD LCD dizains

1. zīmējuma LCD interfeisa laika diagramma

2 datu displeja dizains

2.1 plūsmas shēma

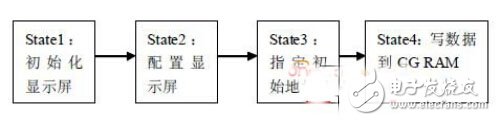

Kā parādīts 2. attēlā, LCD datu displejā ir ieslēgšanas ieslēgšanas inicializācija, konfigurācijas displejs, datu ievadīšana displejā, un sākotnējā adrese jānosaka pirms datu rakstīšanas.

FPGA bāzes LCD LCD dizains

2. attēls LCD displeja plūsmas diagramma

Attīstības plāksnes kristāls ir 50 MHz.